이번에 Zynq 시리즈 FPGA를 이용하면서 알게 된 것들을 정리해보았다. 이쪽 세계는 알아야 하는 게 많지만 그것보다는 컴파일 시간이 너무 오래 걸려서 개발 시간을 다 잡아먹는다… 머리가 좋거나 설계를 처음부터 잘해서 디버깅 할 일을 최대한 줄여야….하는데……… ‘-`)

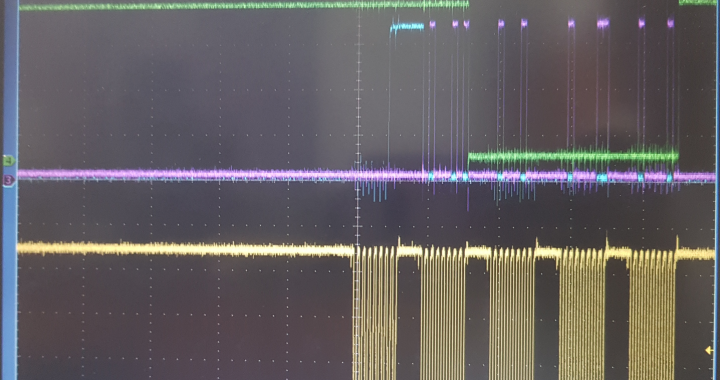

SPI 통신 예제 코드 (Master=Arduino, Slave=Verilog FPGA)

최근에 Xilinx社의 FPGA에서 SPI 통신을 구현하여 동작시킬 일이 있어서 코드를 짜봤습니다.

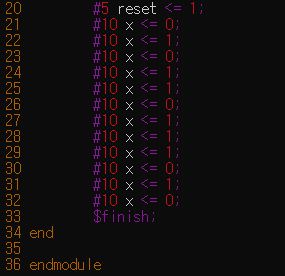

Verilog에서 always가 들어간 테스트 벤치 모듈을 종료시키기

기본적으로 Verilog의 always 블럭은 영원히 돌아가게 되어있다. 그런데 만약 테스트 벤치에 특정 클럭 시점까지의 행동들만 들어있다면 그 이후에는 의미없는 행동이 계속 돌아갈 것이다. 따라서 행동들 마지막에 $finish;를 추가하면 시뮬레이션을 종료할 수 있다.

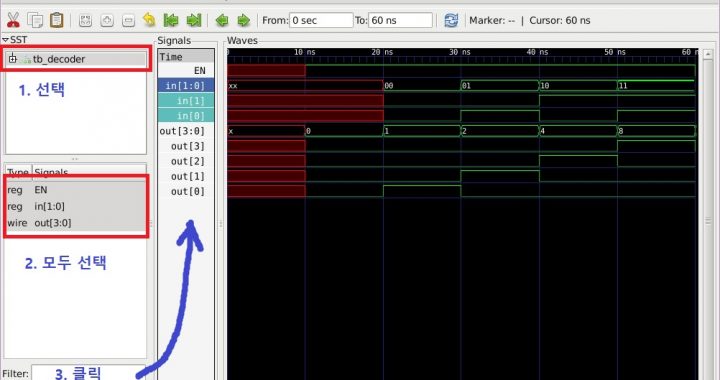

리눅스에서 Verilog 컴파일, 시뮬레이션 및 신호 그래프 확인하기

리눅스에서 verilog 코드를 컴파일, 실행하고 신호 결과를 gtkwave로 확인하는 방법을 설명합니다.