리눅스에선 iverilog를 이용하면 베릴로그 코드를 컴파일 및 시뮬레이션할 수 있으며, FPGA 에 올리는것도 가능은 한 것 같다.

우선 sudo apt-get install을 이용해 iverilog와 gtkwave를 설치한다.

설치한 후에는 테스트 벤치와 각종 모듈을 .v파일을 생성해서 정의한다.

아래는 예시

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

module decoder2( in, out, EN ); input wire [1:0] in; input wire EN; output reg [3:0] out; always @(in or EN) case({EN, in}) 3'b100: out = 4'b0001; 3'b101: out = 4'b0010; 3'b110: out = 4'b0100; 3'b111: out = 4'b1000; default: out = 4'b0000; endcase endmodule |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

`timescale 1ns / 1ps module tb_decoder2( in, out, EN ); input wire [3:0] out; output reg [1:0] in; output reg EN; decoder2 decoder2(.in(in), .out(out), .EN(EN)); initial begin $dumpfile("output.vcd"); $dumpvars(0, tb_decoder2); #10 EN=1; #10 in = 2'b00; #10 in = 2'b01; #10 in = 2'b10; #10 in = 2'b11; #10 EN = 0; end endmodule |

테스트 벤치를 작성할 때 중요한건 initial begin문 직후에 위와 같이 $dumpfile(“output.vcd”); 와 $dumpvars(0, 테스트벤치모듈명); 을 작성해서 각종 입출력의 신호변화가 VCD 파일로 저장되게 해야 한다는 것이다.

작성이 완료되고나면 터미널에서 아래처럼 코드 파일들을 명시하고 iverilog를 실행한다.

iverilog decoder2.v tb_decoder2.v

그러고 나면 a.out이라는 실행파일이 생길것이다. 실행파일명을 미리 지정해주지 않아서 a.out이라는 기본 이름으로 생성된듯. 아무튼 이걸 실행해야 테스트 벤치가 실제로 수행된다. 그때 “VCD info: dumpfile output.vcd opened for output.” 라는 메시지가 콘솔에 출력되면 테스트 벤치가 잘 불러졌다는 것이다.

그러고나서 아래처럼 output.vcd를 지정하여 gtkwave를 실행한다.

gtkwave output.vcd

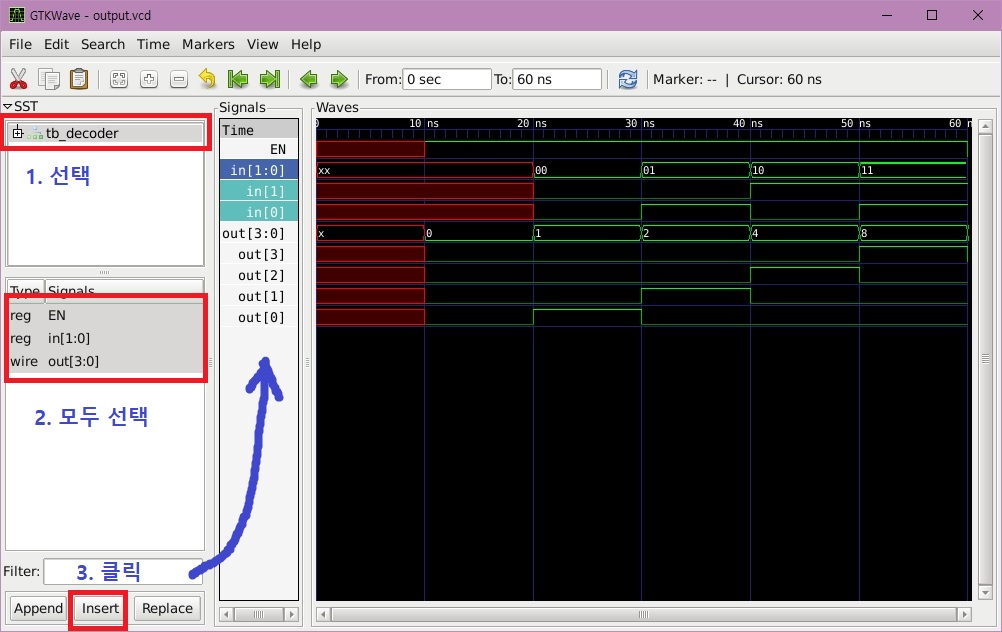

그러면 아래처럼 gtkwave가 해당 파일을 불러오게 되는데, 아래 그림에 표시한 번호대로 선택,선택,클릭하면 신호가 오른쪽 그래프에 나오게 된다. 확대 아이콘 왼쪽에 있는 아이콘을 누르면 신호의 전체길이에 맞게 그래프 시점이 축소된다.